제1세부

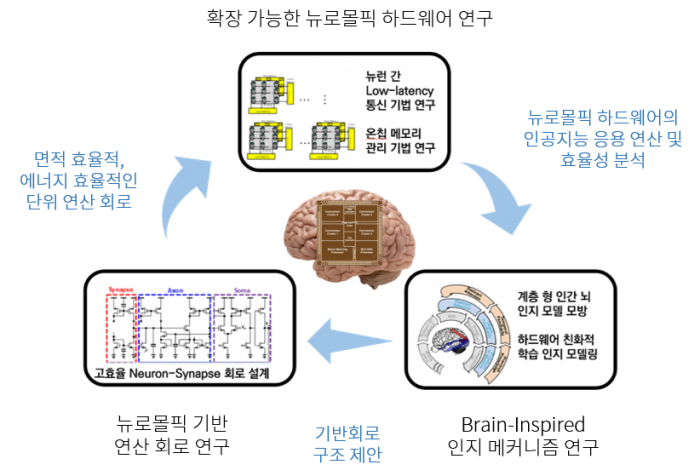

“인간 두뇌의 정보 처리 메커니즘을 모사한 저전력, 고효율 뉴로몰픽 인지 하드웨어 설계”

- 계층화, 모듈화 된 인간 두뇌의 정보 처리 메커니즘을 모사하여 기존 기술의 한계를 극복할 수 있는 저전력, 고효율 뉴로몰픽 인지 하드웨어 설계 (시냅스 13×107개 집적, 60×109 synaptic ops/sec)

- 뉴로몰픽 하드웨어를 제안하고 기존의 CPU, GPU, NPU 등이 갖는 에너지 효율의 한계를 극복하고 인지, 추론, 학습 과정을 탑재하여 인간 뇌의 학습 능력까지 효율적으로 모방하여 결합하는 구조 연구

| 1 단계 : 계층화/모듈화 된 뇌 모방 모델 및 하드웨어 연구 |

|

| 2 단계: 뉴로몰픽 신경망 회로 설계 및 시뮬레이션 |

|

| 3 단계: 기존의 병렬처리 하드웨어를 대체하는 뉴로몰픽 하드웨어 구조 연구 |

|