제4세부

“미래 인공지능 컴퓨팅을 위한 PIM 원천기술 연구”

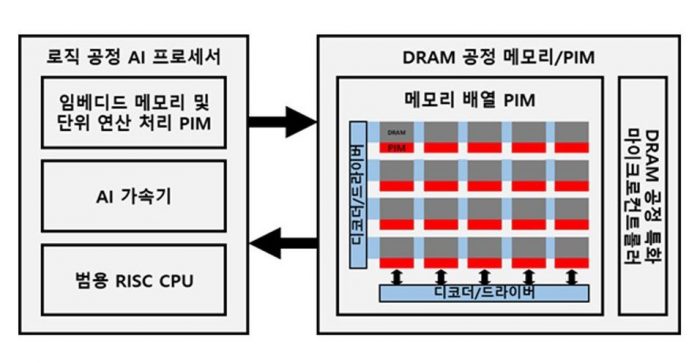

- 차세대 AI 프로세서를 위한 Logic 공정과 DRAM 공정에 기반한 PIM (Processing- In-Memory) 원천기술 개발 및 확보

- DRAM 공정을 활용한 AI 가속기 및 프로세서 설계를 통해 DRAM과 AI 프로세서가 통합된 PIM과 이를 위한 기반 설계기술 연구/개발 및 다양한 응용시스템에 대한 탐색 (연산 집적도: 109 operations / mm2)

- Logic 공정 기반 AI 프로세서와 유기적으로 통신 가능한 PIM Co-processor 기술 연구 (연산 효율성: 1013 operations / W)

| 1 단계 : DRAM공정 활용 ASIC 기반설계기술 연구 |

|

| 2 단계: PIM기반 AI프로세서 원천기술 연구 |

|

| 3 단계: PIM 기반 AI 프로세서 검증 및 응용 개발 연구 |

|