제2세부

“인공지능 컴퓨팅을 위한 기반 아날로그 회로 기술 개발”

- 인공지능 컴퓨팅을 위한 기반 아날로그 회로기술 개발

- 고성능 신호처리 회로 개발

- 저전력 신경망 구현을 위한 아날로그 뉴런 연구 (0.5uJ/classification, CIFAR-10 90% 정확도)

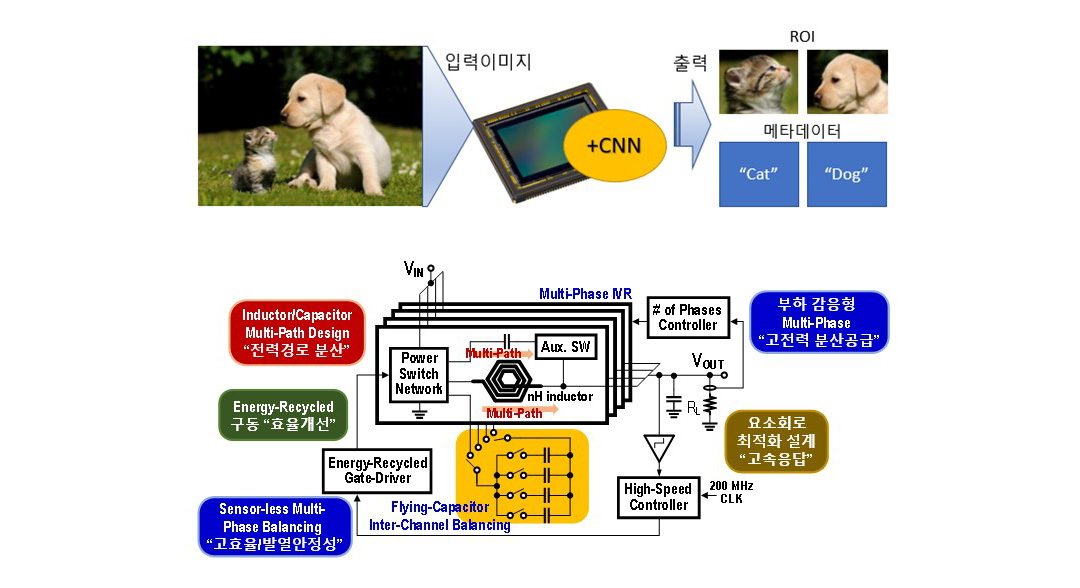

- 고성능 AI 컴퓨팅용 고효율 전력관리 집적회로 개발 (DVS 속도 100ns/V)

| 1 단계 : 아날로그 뉴런 및 고출력 고효율 전력변환기 Topology 도출 |

|

| 2 단계: 아날로그 신경망 구현 및 초고속 DVS를 위한 요소기술 개발 |

|

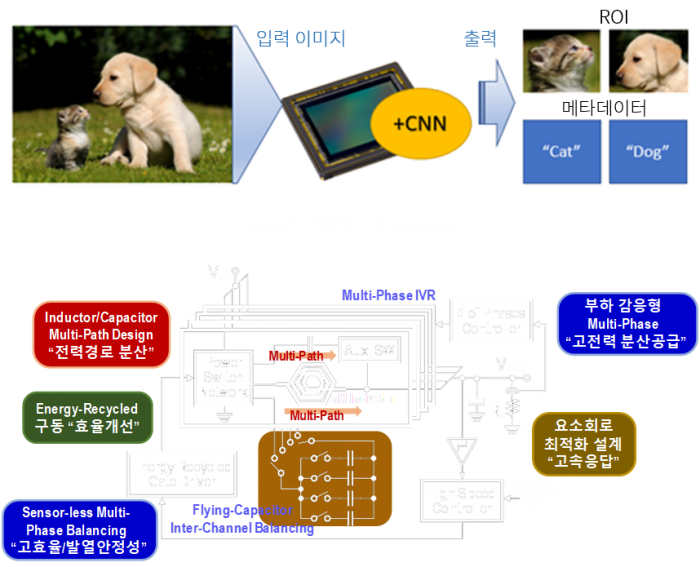

| 3 단계: CNN이 결합된 이미지센서 및 완전집적형 Regulator 개발 |

|